当前课程知识点:EDA技术与应用 > 第四章 VHDL语言概述 > 4.13 条件信号赋值语句 > 4.13.2 条件信号赋值语句 教学视频

同学们,大家好

这一讲我们来学习一种新的并行语句

条件信号赋值语句

通过前面的学习

我们已经知道对信号的赋值

可以通过信号赋值符来完成

这种赋值操作是不附加任何条件的

我们称之为简单信号赋值

简单信号赋值,可以是顺序执行的

也可以是并发执行的

这取决于语句的书写位置

在实际应用中

经常会出现对信号的赋值

需要在满足一定条件的时候才能进行

如果不满足条件,就不赋值的情况

这个时候就需要用到条件信号赋值语句

下面我们来学习一下

条件信号赋值语句的结构和功能

条件信号赋值语句的语法格式是这样的

条件信号赋值语句在执行的时候

首先要进行条件的判断

然后再进行信号的赋值

每一个条件是按照书写顺序逐项测定的

一旦发现某一条WHEN子句中的

条件返回值为true时

就立刻将该子句中的表达式

赋值给目标信号

最后一个表达式可以不带WHEN子句

当所有的条件都不满足的时候

就把表达式n的值赋值给目标信号

下面我们来看一个例子

体会一下条件信号赋值语句的应用

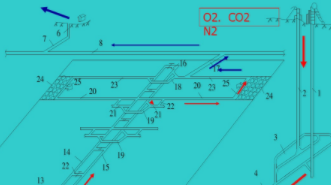

我们来完成一个4选1多路选择器的设计

电路的名称是mux4_1

d3、d2、d1和d0是4个数据输入端

s1和s0是两个地址端

q是数据输出端

电路的功能是根据s1和s0

这两个地址端的不同状态

从d3、d2、d1、d0这四个输入数据中

选择一个输出到q

当地址溢出的时候,电路的输出为高阻态

以下是用条件信号赋值语句

完成的设计代码

代码开始

依然是必要的库声明和程序包声明

然后是实体说明

定义了实体名称和所有的电路端口

结构体没有使用进程

而是采用了条件信号赋值语句

执行的时候,会依次判断各条件是否成立

由此来决定d3、d2、d1和d0

这四个输入数据中

哪一个被选中输出到q

那么根据真值表

我们可以很容易地确定选择条件

和相应的赋值操作之间的对应关系

如果所有的条件都不满足

则说明地址信号溢出

那么就把高阻态Z,赋值到输出端q

需要强调的是

条件信号赋值语句是一种并行语句

因此它不能用于进程、函数或者过程内部

只能用在结构体里面

条件信号赋值语句是一种并发执行的语句

能够根据条件有选择地对目标信号赋值

条件信号赋值语句中的各个条件

必须是布尔表达式

执行时,依次判断各条件的布尔值

当某一个条件满足时

就会对目标信号做相应的赋值

好,本讲到这里就结束了

同学们,再见

-1.1 EDA技术概述

--1.1.3 EDA技术概述 单元测验

-2.1 可编程逻辑器件(PLD)概述

--2.1.3 可编程逻辑器件概述 单元测验

-2.2 CPLD的结构和原理

--2.2.3 CPLD的结构和原理 单元测验

-2.3 FPGA的结构和原理

--2.3.3 FPGA的结构和原理 单元测验

-2.4 FPGA和CPLD的选用

--2.4.3 FPGA和CPLD的选用 单元测验

-2.5 FPGA与CPLD的编程和配置

--2.5.3 FPGA与CPLD的编程与配置 单元测验

-3.1 QuartusII概述

--3.1.3 Quartus Ⅱ概述 单元测验

-3.2 新建工程

--3.2.3 新建工程 单元测验

-3.3 设计输入

--3.3.3 设计输入 单元测验

-3.4 设计编译

--3.4.3 设计编译 单元测验

-3.5 仿真验证

--3.5.3 仿真验证 单元测验

-3.6 器件编程

--3.6.4 器件编程 单元测验

-3.7层次化设计

--3.7.3 层次化设计 单元测验

-3.8 宏功能模块的使用

--3.8.3 宏功能模块的使用 单元测验

-4.1 VHDL语言概述

--4.1.3 VHDL语言概述 单元测验

-4.2 VHDL代码的结构

--4.2.3 VHDL代码的结构 单元测验

-4.3 库和库声明

--4.3.3 库和库声明 单元测验

-4.4 实体说明

--4.4.3 实体说明 单元测验

-4.5 结构体

--4.5.3 结构体 单元测验

-4.6 VHDL预定义数据类型

--4.6.3 VHDL预定义数据类型 单元测验

-4.7 常量、变量和信号

--4.7.3 常量、变量和信号 单元测验

-4.8 运算操作符和属性

--4.8.3 运算操作符和属性 单元测验

-4.9 IF语句和WAIT语句

--4.9.3 IF语句和WAIT语句 单元测验

-4.10 CASE语句

--4.10.3 CASE语句 单元测验

-4.11 LOOP循环语句

--4.11.3 LOOP循环语句 单元测验

-4.12 进程

--4.12.3 进程 单元测验

-4.13 条件信号赋值语句

--4.13.3 条件信号赋值语句 单元测验

-4.14 选择信号赋值语句

--4.14.3 选择信号赋值语句 单元测验

-4.15 元件例化语句

--4.15.3 元件例化语句 单元测验

-4.16 VHDL模块化设计

--4.16.3 VHDL模块化设计 单元测验

-5.1 设计方法概述

--5.1.3 设计方法概述 单元测验

-5.2 EDA综合设计案例(1)— 数字钟的设计

--5.2.2 EDA综合设计设计案例1— 数字钟的设计 教学视频

--5.2.3 EDA综合设计案例1 单元测验

-5.3 EDA综合设计案例(2)—16×16点阵控制器设计

--5.3.2 EDA综合设计案例2—16×16点阵控制器设计 教学视频

--5.3.3 EDA综合设计案例2 单元测验